# COMPUTER INTERFACE FOR TUNING AND CONTROL (CITAC)

#### GENERAL DESCRIPTION

The SAB3036 provides closed-loop digital tuning of TV receivers, with or without a.f.c., as required. It also controls 4 general purpose I/O ports and 4 high-current outputs for tuner band selection.

The IC is used in conjunction with a microcomputer from the MAB8400 family and is controlled via a two-wire, bidirectional I<sup>2</sup>C bus.

#### **Features**

- Combined analogue and digital circuitry minimizes the number of additional interfacing components required

- Frequency measurement with resolution of 50 kHz

- Selectable prescaler divisor of 64 or 256

- 32 V tuning voltage amplifier

- 4 high-current outputs for direct band selection

- Four general purpose input/output (I/O) ports

- Tuning with control of speed and direction

- Tuning with or without a.f.c.

- Single-pin, 4 MHz on-chip oscillator

- I<sup>2</sup>C bus slave transceiver

#### QUICK REFERENCE DATA

| Supply voltages                     |                  |       | ·         |

|-------------------------------------|------------------|-------|-----------|

| (pin 5)                             | V <sub>P1</sub>  | typ.  | 12 V      |

| (pin 14)                            | $V_{P2}$         | typ.  | 13 V      |

| (pin 9)                             | V <sub>P3</sub>  | typ.  | 32 V      |

| supply currents (no outputs loaded) |                  |       |           |

| (pin 5)                             | lP1              | typ.  | 23 mA     |

| (pin 14)                            | 1 <sub>P2</sub>  | typ.  | 0,1 mA    |

| (pin 9)                             | I <sub>P3</sub>  | typ.  | 0,6 mA    |

| Total power dissipation             | $P_{tot}$        | typ.  | 300 mW    |

| Operating ambient temperature range | T <sub>amb</sub> | −20 t | o + 70 °C |

#### **PACKAGE OUTLINE**

18-lead DIL; plastic (SOT102).

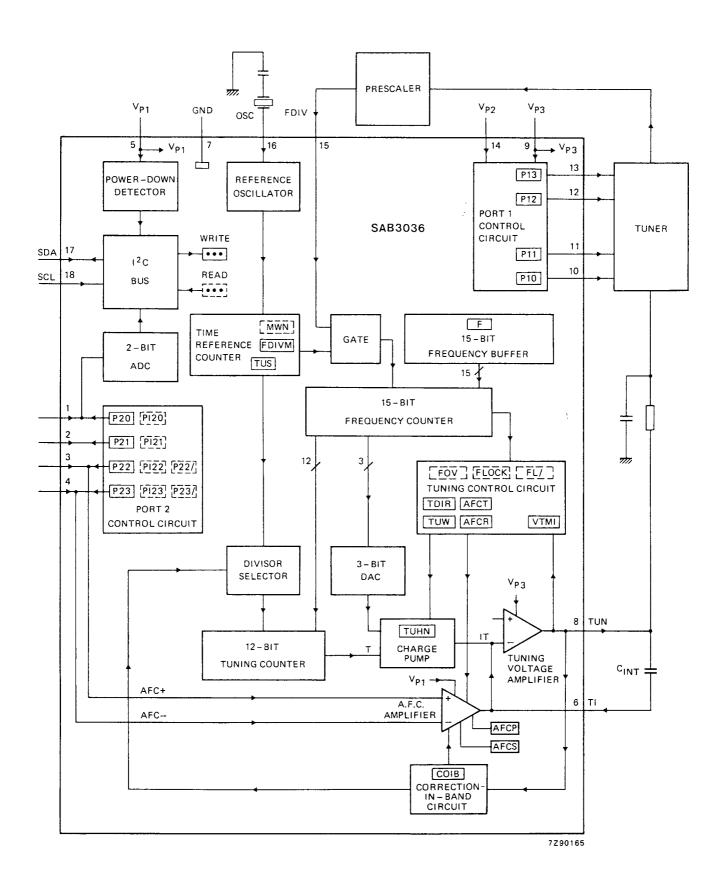

Fig. 1 Block diagram.

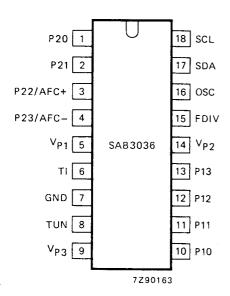

Fig. 2 Pinning diagram.

| PINN | ING             |                                                                 |

|------|-----------------|-----------------------------------------------------------------|

| 1    | P20             | general purpose                                                 |

| 2    | P21 )           | input/output ports                                              |

| 3    | P22/AFC+        | general purpose input/output                                    |

| 4    | P23/AFC-        | ports and a.f.c. inputs                                         |

| 5    | $V_{P1}$        | + 12 V supply voltage                                           |

| 6    | TI              | tuning voltage amplifier inverting input                        |

| 7    | GND             | ground                                                          |

| 8    | TUN             | tuning voltage amplifier output                                 |

| 9    | V <sub>P3</sub> | + 32 V supply for tuning voltage amplifier                      |

| 10   | P10 )           |                                                                 |

| 11   | P11             | high-current band-selection                                     |

| 12   | P12 (           | output ports                                                    |

| 13   | P13             |                                                                 |

| 14   | V <sub>P2</sub> | positive supply for high-current band-selection output circuits |

| 15   | FDIV            | input from prescaler                                            |

| 16   | OSC             | crystal oscillator input                                        |

| 17   | SDA             | serial data line \ \ \lambda^2 C bus                            |

| 18   | SCL             | serial clock line                                               |

Purchase of Philips' I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C-system provided the system conforms to the I<sup>2</sup>C specifications defined by Philips.

#### **FUNCTIONAL DESCRIPTION**

The SAB3036 is a monolithic computer interface which provides tuning and control functions and operates in conjunction with a microcomputer via an I<sup>2</sup>C bus.

## **Tuning**

This is performed using frequency-locked loop digital control. Data corresponding to the required tuner frequency is stored in a 15-bit frequency buffer. The actual tuner frequency, divided by a factor of 256 (or by 64) by a prescaler, is applied via a gate to a 15-bit frequency counter. This input (FDIV) is measured over a period controlled by a time reference counter and is compared with the contents of the frequency buffer. The result of the comparison is used to control the tuning voltage so that the tuner frequency equals the contents of the frequency buffer multiplied by 50 kHz within a programmable tuning window (TUW).

The system cycles over a period of 6,4 ms (or 2,56 ms), controlled by the time reference counter which is clocked by an on-chip 4 MHz reference oscillator. Regulation of the tuning voltage is performed by a charge pump frequency-locked loop system. The charge IT flowing into the tuning voltage amplifier is controlled by the tuning counter, 3-bit DAC and the charge pump circuit. The charge IT is linear with the frequency deviation  $\Delta f$  in steps of 50 kHz. For loop gain control, the relationship  $\Delta IT/\Delta f$  is programmable. In the normal mode (when control bits TUHN0 and TUHN1 are both at logic 1, see OPERATION), the minimum charge IT at  $\Delta f$  = 50 kHz equals 250  $\mu$ A  $\mu$ s (typical).

By programming the tuning sensitivity bits (TUS), the charge IT can be doubled up to 6 times. If correction-in-band (COIB) is programmed, the charge can be further doubled up to three times in relation to the tuning voltage level. From this, the maximum charge IT at  $\Delta f = 50$  kHz equals  $2^6 \times 2^3 \times 250 \,\mu\text{A}$   $\mu\text{S}$  (typical).

The maximum tuning current I is 875  $\mu$ A (typical). In the tuning-hold (TUHN) mode (TUHN is active LOW), the tuning current I is reduced and as a consequence the charge into the tuning amplifier is also reduced.

An in-lock situation can be detected by reading FLOCK. When the tuner oscillator frequency is within the programmable tuning window (TUW), FLOCK is set to logic 1. If the frequency is also within the programmable a.f.c. hold range (AFCR), which always occurs if AFCR is wider than TUW, control bit AFCT can be set to logic 1. When set, digital tuning will be switched off, a.f.c. will be switched on and FLOCK will stay at logic 1 as long as the oscillator frequency is within AFCR. If the frequency of the tuning oscillator does not remain within AFCR, AFCT is cleared automatically and the system reverts to digital tuning. To be able to detect this situation, the occurrence of positive and negative transitions in the FLOCK signal can be read (FL/1N and FL/0N). AFCT can also be cleared by programming the AFCT bit to logic 0.

The a.f.c. has programmable polarity and transconductance; the latter can be doubled up to 3 times, depending on the tuning voltage level if correction-in-band is used.

The direction of tuning is programmable by using control bits TDIRD (tuning direction down) and TDIRU (tuning direction up). If a tuner enters a region in which oscillation stops, then, providing the prescaler remains stable, no FDIV signal is supplied to CITAC. In this situation the system will tune up, moving away from frequency lock-in. This situation is avoided by setting TDIRD which causes the system to tune down. In normal operation TDIRD must be cleared.

If a tuner stops oscillating and the prescaler becomes unstable by going into self-oscillation at a very high frequency, the system will react by tuning down, moving away from frequency lock-in. To overcome this, the system can be forced to tune up at the lowest sensitivity (TUS) value, by setting TDIRU.

Setting both TDIRD and TDIRU causes the digital tuning to be interrupted and a.f.c. to be switched on.

The minimum tuning voltage which can be generated during digital tuning is programmable by VTMI to prevent the tuner being driven into an unspecified low tuning voltage region.

#### Control

For tuner band selection there are four outputs P10 to P13 which are capable of sourcing up to 50 mA at a voltage drop of less than 600 mV with respect to the separate power supply input Vp2.

For additional digital control, four open collector I/O ports P20 to P23 are provided. Ports P22 and P23 are capable of detecting positive and negative transitions in their input signals and are connected with the AFC+ and AFC- inputs respectively. The a.f.c. amplifier must be switched off when P22 and/or P23 are used. When a.f.c. is used, P22 and P23 must be programmed HIGH (high impedance state). With the aid of port P20, up to three independent module addresses can be programmed.

## Reset

CITAC goes into the power-down-reset mode when V<sub>P1</sub> is below 8,5 V (typical). In this mode all registers are set to a defined state. Reset can also be programmed.

#### **OPERATION**

#### Write

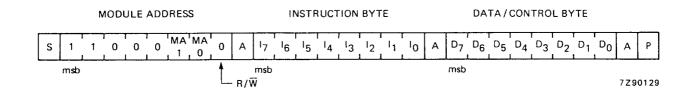

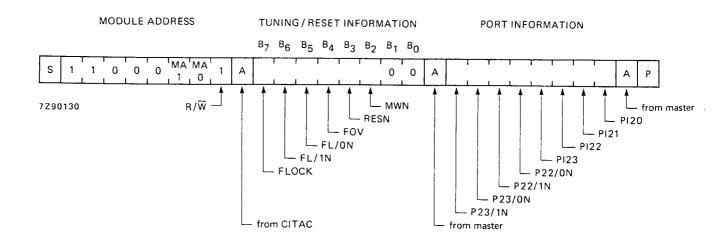

CITAC is controlled via a bidirectional two-wire  $I^2C$  bus; the  $I^2C$  bus is specified in our data handbook "ICs for digital systems in radio, audio, and video equipment". For programming, a module address,  $R/\overline{W}$  bit (logic 0), an instruction byte and a data/control byte are written into CITAC in the format shown in Fig. 3.

Fig. 3 12 C bus write format.

The module address bits MA1, MA0 are used to give a 2-bit module address as a function of the voltage at port P20 as shown in Table 1.

Acknowledge (A) is generated by CITAC only when a valid address is received and the device is not in the power-down-reset mode ( $V_{P1} > 8,5 \text{ V (typical)}$ ).

# **OPERATION** (continued)

Table 1 Valid module addresses

| MA1 | MAO | P20        |

|-----|-----|------------|

| O   | 0   | don't care |

| O   | 1   | GND        |

| 1   | 0   | ½Vp1       |

| 1   | 1   | Vp1        |

#### **Tuning**

Tuning is controlled by the instruction and data/control bytes as shown in Fig. 4.

INSTRUCTION BYTE

|       |    |     | 11/ | ISTRUCT | TON BY | TE  |    |    |                |                | DA <sup>*</sup> | TA/CON                                 | TROL B | YTE            |                |                |

|-------|----|-----|-----|---------|--------|-----|----|----|----------------|----------------|-----------------|----------------------------------------|--------|----------------|----------------|----------------|

|       | 17 | 16  | 15  | 14      | 13     | 12  | 11 | 10 | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub>  | 04                                     | D3     | D <sub>2</sub> | D <sub>1</sub> | D <sub>O</sub> |

| freq. | 1  | F14 | F13 | F12     | F11    | F10 | F9 | F8 | F7             | F6             | F5              | F4                                     | F3     | F2             | F1             | F0             |

| TCD0  | 0  | 0   | 1   | 0       | 1      | 0   | 0  | 1  | AFCT           | VTMI0          | AFCR1           | AFCR0                                  | TUHN1  | TUHNO          | TUW1           | TUWO           |

| TCD1  | 0  | 0   | 1   | 0       | 1      | 0   | 1  | o  | VTMI1          | COIB1          | COIBO           | AFCS1                                  | AFCS 0 | TUS 2          | TUS1           | TUSO           |

| TCD2  | 0  | 0   | 1   | 0       | 1      | 0   | 1  | 1  | 0              | 0              | 0               | 0                                      | AFCP   | FDIVM          | TDIRD          | TDIRU          |

|       |    |     |     |         |        | ·   |    |    | L              |                | L               | ــــــــــــــــــــــــــــــــــــــ |        |                |                | ل              |

Fig. 4 Tuning control format.

# 7Z90125

# Frequency

Frequency is set when bit 17 of the instruction byte is set to logic 1; the remainder of this byte together with the data/control byte are loaded into the frequency buffer. The frequency to which the tuner oscillator is regulated equals the decimal representation of the 15-bit word multiplied by 50 kHz. All frequency bits are set to logic 1 at reset.

# Tuning hold

The TUHN bits are used to decrease the maximum tuning current and, as a consequence, the minimum charge IT (at  $\Delta f = 50$  kHz) into the tuning amplifier.

Table 2 Tuning current control

| TUHN1 | TUHN0 | typ. I <sub>max</sub><br>μΑ | typ. lT <sub>min</sub><br>μΑ μs | typ. $\Delta V_{TUNmin}$ at $C_{INT} = 1 \mu F$ $\mu V$ |

|-------|-------|-----------------------------|---------------------------------|---------------------------------------------------------|

| 0     | 0     | 3,5*                        | 1*                              | 1*                                                      |

| 0     | 1     | 29                          | 8                               | 8                                                       |

| 1     | 0     | 110                         | 30                              | 30                                                      |

| 1     | 1     | 875                         | 250                             | 250                                                     |

<sup>\*</sup> Values after reset.

During tuning but before lock-in, the highest current value should be selected. After lock-in the current may be reduced to decrease the tuning voltage ripple.

The lowest current value should not be used for tuning due to the input bias current of the tuning voltage amplifier (max. 5 nA). However it is good practice to program the lowest current value during tuner band switching.

# Tuning sensitivity

To be able to program an optimum loop gain, the charge IT can be programmed by changing T using tuning sensitivity (TUS). Table 3 shows the minimum charge IT obtained by programming the TUS bits at  $\Delta f = 50 \text{ kHz}$ ; TUHN0 and TUHN1 = logic 1.

Table 3 Minimum charge IT as a function of TUS

$\Delta f = 50 \text{ kHz}$ ; TUHN0 = logic 1; TUHN1 = logic 1

| TUS2 | TUS1 | TUS0 | typ. IT <sub>min</sub><br>mA μs | typ. $\Delta V_{TUNmin}$ at $C_{INT} = 1 \mu F$ mV |

|------|------|------|---------------------------------|----------------------------------------------------|

| 0    | 0    | 0    | 0,25*                           | 0,25*                                              |

| 0    | 0    | 1    | 0,5                             | 0,5                                                |

| 0    | 1    | 0    | 1                               | 1                                                  |

| 0    | 1    | 1    | 2                               | 2                                                  |

| 1    | 0    | 0    | 4                               | 4                                                  |

| 1    | 0    | 1    | 8                               | 8                                                  |

| 1    | 1    | 0    | 16                              | 16                                                 |

<sup>\*</sup> Values after reset.

#### Correction-in-band

This control is used to correct the loop gain of the tuning system to reduce in-band variations due to a non-linear voltage/frequency characteristic of the tuner. Correction-in-band (COIB) controls the time T of the charge equation IT and takes into account the tuning voltage V<sub>TUN</sub> to give charge multiplying factors as shown in Table 4.

Table 4 Programming correction-in-band

| COIB1 | COIBO |        | Itiplying factors at t |            | . •    |

|-------|-------|--------|------------------------|------------|--------|

|       |       | < 12 V | 12 to 18 V             | 18 to 24 V | > 24 V |

| 0     | 0     | 1*     | 1*                     | 1*         | 1*     |

| 0     | 1     | 1      | 1                      | 1          | 2      |

| 1     | 0     | 1      | 1                      | 2          | 4      |

| 1     | 1     | 1      | 2                      | 4          | 8      |

<sup>\*</sup> Values after reset.

The transconductance multiplying factor of the a.f.c. amplifier is similar when COIB is used, except for the lowest transconductance which is not affected.

# Tuning window

Digital tuning is interrupted and FLOCK is set to logic 1 (in-lock) when the absolute deviation  $|\Delta f|$  between the tuner oscillator frequency and the programmed frequency is smaller than the programmed TUW value (see Table 5). If  $|\Delta f|$  is up to 50 kHz above the values listed in Table 5, it is possible for the system to be locked depending on the phase relationship between FDIV and the reference counter.

# **OPERATION** (continued)

Table 5 Tuning window programming

| TUW1 | TUWO | Δf  (kHz) | tuning window (kHz) |

|------|------|-----------|---------------------|

| 0    | 0    | 0*        | 0*                  |

| 0    | 1    | 50        | 100                 |

| 1    | 0    | 150       | 300                 |

<sup>\*</sup> Values after reset.

#### A.F.C.

When AFCT is set to logic 1 it will not be cleared and the a.f.c. will remain on as long as  $|\Delta f|$  is less than the value programmed for the a.f.c. hold range AFCR (see Table 6). It is possible for the a.f.c. to remain on for values of up to 50 kHz more than the programmed value depending on the phase relationship between FDIV and the reference counter.

Table 6 A.F.C. hold range programming

| AFCR1 | AFCR0 | Δf  (kHz) | a.f.c. hold range (kHz) |

|-------|-------|-----------|-------------------------|

| 0     | 0     | 0*        | 0*                      |

| 0     | 1     | 350       | 700                     |

| 1     | 0     | 750       | 1500                    |

<sup>\*</sup> Values after reset.

#### Transconductance

The transconductance (g) of the a.f.c. amplifier is programmed via the a.f.c. sensitivity bits AFCS as shown in Table 7.

Table 7 Transconductance programming

| AFCS1 | AFCS0 | typ. transconductance (μΑ/V) |

|-------|-------|------------------------------|

| 0     | 0     | 0,25*                        |

| 0     | 1     | 25                           |

| 1     | 0     | 50                           |

| 1     | 1     | 100                          |

<sup>\*</sup> Value after reset.

#### A.F.C. polarity

If a positive differential input voltage is applied to the (switched on) a.f.c. amplifier, the tuning voltage  $V_{TUN}$  falls when the a.f.c. polarity bit AFCP is at logic 0 (value after reset). At AFCP = logic 1,  $V_{TUN}$  rises.

# Minimum tuning voltage

Both minimum tuning voltage control bits, VTMI1 and VTMI0, are at logic 0 after reset. Further details are given in CHARACTERISTICS.

# Frequency measuring window

The frequency measuring window which is programmed must correspond with the division factor of the prescaler in use (see Table 8).

Table 8 Frequency measuring window programming

| FDIVM | prescaler division factor | cycle period (ms) | measuring window (ms) |

|-------|---------------------------|-------------------|-----------------------|

| 0     | 256                       | 6,4*              | 5,12*                 |

|       | 64                        | 2,56              | 1,28                  |

<sup>\*</sup> Values after reset.

# Tuning direction

Both tuning direction bits, TDIRU (up) and TDIRD (down), are at logic 0 after reset.

#### Control

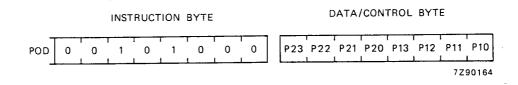

The instruction byte POD (port output data) is shown in Fig. 5, together with the corresponding data/ control byte. Control is implemented as follows:

P13, P12, P11, P10

Band select outputs. If a logic 1 is programmed on any of the POD bits D<sub>3</sub> to D<sub>0</sub>, the relevant output goes HIGH. All outputs are LOW after reset.

P23, P22, P21, P20

Open collector I/O ports. If a logic 0 is programmed on any of the POD bits D7 to D4, the relevant output is forced LOW. All outputs are at logic 1 after reset (high impedance state).

Fig. 5 Control programming.

# **OPERATION** (continued)

#### Read

Information is read from CITAC when the R/W bit is set to logic 1. An acknowledge must be generated by the master after each data byte to allow transmission to continue. If no acknowledge is generated by the master the slave (CITAC) stops transmitting. The format of the information bytes is shown in Fig. 6.

Fig. 6 Information byte format.

# Tuning/reset information bits

| •     |                                                                                                                                                                                                                                                                                              |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FLOCK | Set to logic 1 when the tuning oscillator frequency is within the programmed tuning window.                                                                                                                                                                                                  |

| FL/1N | Set to logic 0 (active LOW) when FLOCK changes from 0 to 1 and is reset to logic 1 automatically after tuning information has been read.                                                                                                                                                     |

| FL/0N | As for $FL/1N$ but is set to logic 0 when $FLOCK$ changes from 1 to 0.                                                                                                                                                                                                                       |

| FOV   | Indicates frequency overflow. When the tuner oscillator frequency is too high with respect to the programmed frequency, FOV is at logic 1, and when too low, FOV is at logic 0. FOV is not valid when TDIRU and/or TDIRD are set to logic 1.                                                 |

| RESN  | Set to logic 0 (active LOW) by a programmed reset or a power-down-reset. It is reset to logic 1 automatically after tuning/reset information has been read.                                                                                                                                  |

| MWN   | MWN (frequency measuring window, active LOW) is at logic 1 for a period of 1,28 ms, during which time the results of frequency measurement are processed. This time is independent of the cycle period. During the remaining time, MWN is at logic 0 and the received frequency is measured. |

|       | When slightly different frequencies are programmed repeatedly and a.f.c. is switched on, the received frequency can be measured using FOV and FLOCK.                                                                                                                                         |

To prevent the frequency counter and frequency buffer being loaded at the same time, frequency should be programmed only during the period of MWN = logic 0.

#### Port information bits

| P23/1N, P22/1N            | Set to logic 0 (active LOW) at a LOW-to-HIGH transition in the input voltage on P23 and P22 respectively. Both are reset to logic 1 after the port information has been read. |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P23/0N, P22/0N            | As for P23/1N and P22/1N but are set to logic 0 at a HIGH-to-LOW transition.                                                                                                  |

| PI23, PI22, PI21,<br>PI20 | Indicate input voltage levels at P23, P22, P21 and P20 respectively. A logic 1 indicates a HIGH input level.                                                                  |

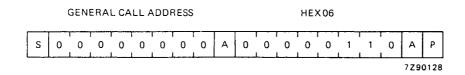

#### Reset

The programming to reset all registers is shown in Fig. 7. Reset is activated only at data byte HEX 06. Acknowledge is generated at every byte, provided that CITAC is not in the power-down-reset mode. After the general call address byte, transmission of more than one data byte is not allowed.

Fig. 7 Reset programming.

#### ·RATINGS

Limiting values in accordance with the Absolute Maximum System (IEC 134)

|  | Supply | / voltage | ranges: |

|--|--------|-----------|---------|

|--|--------|-----------|---------|

| (pin 5)                       | V <sub>P1</sub>                         | -0,3 to + 18 V               |

|-------------------------------|-----------------------------------------|------------------------------|

| (pin 14)                      | V <sub>P2</sub>                         | −0,3 to + 18 V               |

| (pin 9)                       | V <sub>P3</sub>                         | -0,3 to + 36 V               |

| Input/output voltage ranges:  |                                         |                              |

| (pin 17)                      | $V_{SDA}$                               | -0,3 to + 18 V               |

| (pin 18)                      | $v_{SCL}$                               | -0,3 to + 18 V               |

| (pins 1 and 2)                | V <sub>P20</sub> , P21                  | −0,3 to + 18 V               |

| (pins 3 and 4)                | V <sub>P22</sub> , <sub>P23</sub> , AFC | –0,3 to V <sub>P1</sub> * V  |

| (pin 6)                       | $v_{TI}$                                | -0,3 to V <sub>P1</sub> * V  |

| (pin 8)                       | $V_{TUN}$                               | –0,3 to V <sub>P3</sub> * V  |

| (pins 10 to 13)               | V <sub>P1X</sub>                        | –0,3 to V <sub>P2</sub> ** V |

| (pin 15)                      | $v_{FDIV}$                              | –0,3 to V <sub>P1</sub> * V  |

| (pin 16)                      | Vosc                                    | −0,3 to + 5 V                |

| Total power dissipation       | $P_{tot}$                               | max. 1000 mW                 |

| Storage temperature range     | $T_{stg}$                               | -55 to + 125 °C              |

| Operating ambient temperature | $T_{amb}$                               | -20 to + 70 °C               |

- \* Pin voltage may exceed supply voltage if current is limited to 10 mA.

- \*\* Pin voltage must not exceed 18 V but may exceed V<sub>P2</sub> if current is limited to 200 mA.

# CHARACTERISTICS

$T_{amb}$  = 25 °C;  $V_{P1}$ ,  $V_{P2}$ ,  $V_{P3}$  at typical voltages, unless otherwise specified

| parameter                                           | symbol           | min. | typ. | max.               | unit |

|-----------------------------------------------------|------------------|------|------|--------------------|------|

| Supply voltages                                     | V <sub>P1</sub>  | 10,5 | 12   | 13,5               | V    |

|                                                     | V <sub>P2</sub>  | 4,7  | 13   | 16                 | V    |

|                                                     | V <sub>P3</sub>  | 30   | 32   | 35                 | V    |

| Supply currents (no outputs loaded)                 | I <sub>P1</sub>  | 14   | 23   | 40                 | mA   |

|                                                     | I <sub>P2</sub>  | 0    |      | 0,1                | mA   |

|                                                     | I <sub>P3</sub>  | 0,2  | 0,6  | 2                  | mA   |

| Additional supply currents (A)                      | IP2A             | -2   | _    | IOHP1X             | mA   |

| (note 1)                                            | IP3A             | 0,2  | _    | 2                  | mA   |

| Total power dissipation                             | P <sub>tot</sub> | _    | 300  | _                  | mW   |

| Operating ambient temperature                       | T <sub>amb</sub> | -20  | _    | + 70               | oC.  |

| I <sup>2</sup> C bus inputs/outputs                 |                  |      |      |                    |      |

| SDA input (pin 17);<br>SCL input (pin 18)           |                  |      |      |                    |      |

| Input voltage HIGH (note 2)                         | VIH              | 3    | _    | V <sub>P1</sub> -1 | V    |

| Input voltage LOW                                   | VIL              | -0,3 | _    | 1,5                | V    |

| Input current HIGH (note 2)                         | ΙΙΗ              |      |      | 10                 | μΑ   |

| Input current LOW (note 2)                          | IIL              | _    | _    | 10                 | μΑ   |

| SDA output (pin 17, open collector)                 |                  |      |      |                    |      |

| Output voltage LOW at $I_{OL} = 3 \text{ mA}$       | VOL              | _    | _    | 0,4                | V    |

| Maximum output sink current                         | IOL              |      | 5    |                    | mΑ   |

| Open collector I/O ports                            |                  |      |      |                    |      |

| P20, P21, P22, P23<br>(pins 1 to 4, open collector) |                  |      |      |                    |      |

| Input voltage HIGH (P20, P21)                       | VIH              | 2    | _    | 16                 | V    |

| Input voltage HIGH (P22, P23) AFC switched off      | VIH              | 2    |      | V <sub>P1</sub> -2 | V    |

| Input voltage LOW                                   | VIL              | -0,3 |      | 0,8                | V    |

| Input current HIGH                                  | ЧН               |      | _    | 25                 | μΑ   |

| Input current LOW                                   | -116             | _    |      | 25                 | μΑ   |

| Output voltage LOW at IOL = 2 mA                    | VOL              | _    | _    | 0,4                | V    |

| Maximum output sink current                         | lOL              | -    | 4    |                    | mΑ   |

| parameter                                                                                                                             | symbol                   | min.                  | typ.                   | max.                   | unit                         |

|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------|------------------------|------------------------|------------------------------|

| A.F.C. amplifier                                                                                                                      |                          |                       |                        |                        |                              |

| Inputs AFC+, AFC— (pins 3, 4)                                                                                                         |                          |                       |                        |                        |                              |

| Transconductance for input voltages up to 1 V differential:                                                                           |                          |                       |                        |                        |                              |

| AFCS1 AFCS2 0 0 0 1 1 0 1 1                                                                                                           | 900<br>901<br>910<br>911 | 100<br>15<br>30<br>60 | 250<br>25<br>50<br>100 | 800<br>35<br>70<br>140 | nA/V<br>μΑ/V<br>μΑ/V<br>μΑ/V |

| Tolerance of transconductance multiplying factor (2, 4 or 8) when correction-in-band is used                                          | $\Delta M_q$             | -20                   |                        | + 20                   | %                            |

| Input offset voltage                                                                                                                  | V <sub>loff</sub>        | 75                    | _                      | + 75                   | mV                           |

| Common mode input voltage                                                                                                             | V <sub>com</sub>         | 3                     | _                      | V <sub>P1</sub> -2,5   | V                            |

| Common mode rejection ratio                                                                                                           | CMRR                     | _                     | 50                     |                        | dB                           |

| Power supply (V <sub>P1</sub> ) rejection ratio                                                                                       | PSRR                     |                       | 50                     | _                      | dB                           |

| Input current (P22 and P23 programmed HIGH)                                                                                           | l <sub>l</sub>           | -                     | _                      | 500                    | nΑ                           |

| Tuning voltage amplifier                                                                                                              |                          |                       |                        | 1                      |                              |

| Input TI, output TUN (pins 6, 8)  Maximum output voltage at  Iload = ±1,5 mA  Minimum output voltage at  Iload = ±1,5 mA  VTMI1 VTMI0 | VTUN                     | V <sub>P3</sub> -1,6  | _                      | V <sub>P3</sub> -0,4   | V                            |

| 0 0                                                                                                                                   | VTM00                    | 300                   | _                      | 500                    | mV                           |

| 1 0<br>1 1                                                                                                                            | $V_{TM10}$               | 450                   | _                      | 650                    | mV                           |

| · ·                                                                                                                                   | VTM11                    | 650                   |                        | 900                    | mV                           |

| Maximum output source current                                                                                                         | <sup>-I</sup> TUNH       | 2,5                   | -                      | 8                      | mA                           |

| Maximum output sink current                                                                                                           | <sup>I</sup> TUNL        |                       | 40                     |                        | mA                           |

| Input bias current Power supply (V <sub>P3</sub> ) rejection ratio                                                                    | <sup>I</sup> TI<br>PSRR  | _5<br>_               | -<br>60                | +5<br>-                | nA<br>dB                     |

# CHARACTERISTICS (continued)

| parameter                                                                                   | symbol                               | min.                   | typ.                    | max.                     | unit                    |

|---------------------------------------------------------------------------------------------|--------------------------------------|------------------------|-------------------------|--------------------------|-------------------------|

| Tuning voltage amplifier (continued)                                                        |                                      |                        |                         |                          |                         |

| Minimum charge IT to tuning voltage amplifier                                               |                                      |                        |                         |                          |                         |

| TUHN1 TUHN0<br>0 0<br>0 1                                                                   | CH <sub>00</sub><br>CH <sub>01</sub> | 0,4                    | 1 8                     | 1,7                      | μΑ μς                   |

| 1 O 1                                                                                       | CH <sub>10</sub><br>CH <sub>11</sub> | 15<br>130              | 30<br>250               | 48<br>370                | μΑ μs<br>μΑ μs<br>μΑ μs |

| Tolerance of charge (or $\Delta V_{TUN}$ ) multiplying factor when COIB and/or TUS are used | ΔСН                                  | -20                    |                         | +20                      | %                       |

| Maximum current I into tuning amplifier                                                     |                                      |                        |                         |                          |                         |

| TUHN1 TUHN0 0 0 0 1 1 0 1 1                                                                 | T00<br>T01<br>T10<br>T11             | 1,7<br>15<br>65<br>530 | 3,5<br>29<br>110<br>875 | 5,1<br>41<br>160<br>1220 | μΑ<br>μΑ<br>μΑ<br>μΑ    |

| Correction-in-band                                                                          |                                      |                        |                         |                          |                         |

| Tolerance of correction-in-band levels 12 V, 18 V and 24 V                                  | ΔV <sub>CIB</sub>                    | <b>–15</b>             | _                       | + 15                     | %                       |

| Band-select output ports                                                                    |                                      |                        |                         |                          |                         |

| P10, P11, P12, P13 (pins 10 to 13)                                                          |                                      |                        |                         |                          |                         |

| Output voltage HIGH at —IOH = 50 mA (note 3)                                                | Voн                                  | V <sub>P2</sub> 0,6    | _                       | _                        | v .                     |

| Output voltage LOW at $I_{OL} = 2 \text{ mA}$                                               | VOL                                  | -                      | _                       | 0,4                      | V                       |

| Maximum output source current (note 3)                                                      | <sup>-1</sup> он                     | -                      | 130                     | 200                      | mA                      |

| Maximum output sink current                                                                 | lOL                                  |                        | 5                       | -                        | mA                      |

| FDIV input (pin 15)                                                                         |                                      |                        |                         |                          |                         |

| Input voltage (peak-to-peak value)                                                          |                                      | 0.1                    |                         |                          |                         |

| (t <sub>rise</sub> and t <sub>fall</sub> ≤ 40 ns) Duty cycle                                | VFDIV(p-p)                           | 40                     | -                       | 2                        | V                       |

| Maximum input frequency                                                                     | f                                    | 16                     | _                       | 60                       | %<br>MU-                |

| Input impedance                                                                             | fmax<br>Z <sub>i</sub>               | 10                     | 0                       |                          | MHz                     |

| Input capacitance                                                                           | C <sub>i</sub>                       | _                      | 8<br>5                  | _                        | kΩ<br>pF                |

| parameter                              |                                                      | symbol          | min.                        | typ. | max.                                  | unit   |

|----------------------------------------|------------------------------------------------------|-----------------|-----------------------------|------|---------------------------------------|--------|

| OSC input (pin 24)                     |                                                      |                 |                             |      |                                       |        |

| Crystal resistanc                      | e at resonance (4 MHz)                               | RX              | _                           | _    | 150                                   | Ω      |

| Power-down-rese                        | et                                                   | i<br>           |                             | 1    |                                       |        |

| Maximum supply<br>power-down-r         | y voltage V <sub>P1</sub> at which<br>eset is active | V <sub>PD</sub> | 7,5                         | _    | 9,5                                   | V      |

| Vp1 rise-time du<br>(up to VpD)        | ring power-up                                        | t <sub>r</sub>  | 5                           |      |                                       | μs     |

| Voltage level for valid module address |                                                      |                 |                             |      |                                       |        |

|                                        | P20 (pin 1) for valid module unction of MA1, MA0     |                 |                             |      |                                       |        |

| MA1                                    | MA0                                                  |                 |                             |      |                                       |        |

| 0                                      | 0                                                    | VVA00           | -0,3                        | -    | 16                                    | V      |

| 0                                      | 1                                                    | VVA01           |                             | -    | 0,8                                   | V      |

| 1                                      | 1                                                    | VVA10<br>VVA11  | 2,5<br>V <sub>P1</sub> -0,3 | _    | V <sub>P1</sub> -2<br>V <sub>P1</sub> | V<br>V |

# Notes to the characteristics

- 1. For each band-select output which is programmed at logic 1, sourcing a current IOHP1X, the additional supply currents (A) shown must be added to IP2 and IP3 respectively.

- 2. If  $V_{P1}$  < 1 V, the input current is limited to 10  $\mu A$  at input voltages up to 16 V.

- 3. At continuous operation the output current should not exceed 50 mA. When the output is short-circuited to ground for several seconds the device may be damaged.

- 4. Values are proportional to Vp1.

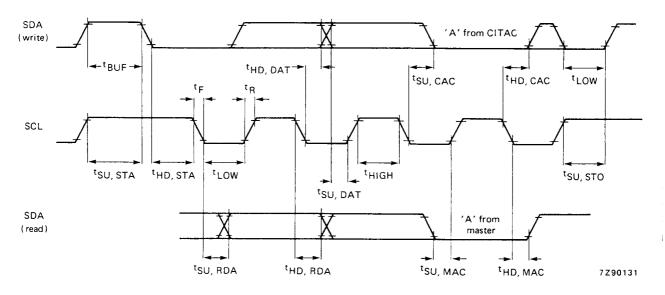

# I<sup>2</sup>C BUS TIMING (Fig. 8)

I<sup>2</sup> C bus load conditions are as follows:

4 k $\Omega$  pull-up resistor to +5 V; 200 pF capacitor to GND.

All values are referred to  $V_{IH} = 3 \text{ V}$  and  $V_{IL} = 1.5 \text{ V}$ .

| parameter                             | symbol              | min.         | typ. | max. | unit |

|---------------------------------------|---------------------|--------------|------|------|------|

| Bus free before start                 | t <sub>BUF</sub>    | 4            | _    | _    | μς   |

| Start condition set-up time           | t <sub>SU,STA</sub> | 4            | _    | _    | μs   |

| Start condition hold time             | tHD,STA             | 4            | _    | _    | μs   |

| SCL, SDA LOW period                   | tLOW                | 4            | _    | _    | μs   |

| SCL HIGH period                       | tHIGH               | 4            |      |      | μs   |

| SCL, SDA rise time                    | t <sub>R</sub>      | <u> </u>     | _    | 1    | μs   |

| SCL, SDA fall time                    | tբ                  | -            | _    | 0,3  | μs   |

| Data set-up time (write)              | tSU,DAT             | 1            | _    | _    | μs   |

| Data hold time (write)                | tHD,DAT             | 1            | _    | _    | μs   |

| Acknowledge (from CITAC) set-up time  | tSU,CAC             | <del>-</del> |      | 2    | μs   |

| Acknowledge (from CITAC) hold time    | tHD,CAC             | 0            | _    | _    | μs   |

| Stop condition set-up time            | tsu,sto             | 4            | _    |      | μs   |

| Data set-up time (read)               | tSU,RDA             | -            | _    | 2    | μs   |

| Data hold time (read)                 | tHD,RDA             | 0            | _    |      | μs   |

| Acknowledge (from master) set-up time | tSU,MAC             | 1            | -    | _    | μs   |

| Acknowledge (from master) hold time   | tHD, MAC            | 2            |      | _    | μs   |

# Note

Timings  $t_{SU,DAT}$  and  $t_{HD,DAT}$  deviate from the  $I^2C$  bus specification . After reset has been activated, transmission may only be started after a 50  $\mu$ s delay.

Fig. 8 12 C bus timing SAB3036.